11111111

CHANNE

# **GENIE-FC™** FC VERIFICATION IP

## **OVERVIEW**

The Genie-FC^{\rm TM} Verification IP Products are the industry's most comprehensive verification solution for FC based designs. Its intelligent Verification Engine, integrated Interface Inspector and comprehensive Compliance Suite provide the perfect combination of tools to ensure first silicon success.

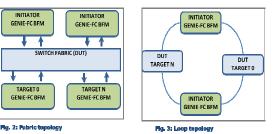

The Genie-FC<sup>™</sup> VIP provides a quick and efficient way to verify any FC based design- Initiator, Switch or Target. It supports FC 1.1, 2 and 3 specifications and tests all layers of the FC protocol -FC-0, FC-1, FC-2, FC-3, & FC-4. Genie-FC provides a complete verification solution that includes multi-language support and UVM, OVM and VMM methodologies.

T

The Genie-FC<sup>™</sup> VIP provides:

- Initiator & Target Models

- Directed and Random Transaction Generator

- Frame & Primitive Generator

- Error Injector & Callbacks

- Monitor/Checker

- Report Generator

- Scoreboard

- Functional Coverage

## **FEATURES**

| <ul> <li>Initiator and Target models for complete FC<br/>Verification of Initiators, Targets and Switches</li> </ul>              | <ul> <li>Verifies all protocol layers (FC-0, FC-1, FC-2,<br/>and FC-4)</li> </ul>                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Supports serial (1 bit) and parallel<br/>(10/16/20/32/40 bit) interface</li> </ul>                                       | <ul> <li>SAM-3/4 Application level exerciser for<br/>System level and block level testing</li> </ul>                |

| <ul> <li>Supports link speeds 1/2/4/8/10/16/20/32G<br/>with Speed Negotiations</li> </ul>                                         | <ul> <li>Supports 8b10b as well as 64b66b encoding</li> <li>&amp; decoding</li> </ul>                               |

| <ul> <li>8 bit Encoder / Decoder interface, Dword level<br/>transport interface, Frame transaction level<br/>interface</li> </ul> | <ul> <li>Automated FC Traffic generation in each<br/>layer</li> <li>Disparity &amp; Kcode/Dcode Checking</li> </ul> |

| <ul> <li>Protocol Checker – functionality at all layers</li> </ul>                                                                | <ul> <li>Support for Configurable L, N, and F ports</li> </ul>                                                      |

| Scoreboard capability for data integrity checking                                                                                 | <ul> <li>Supports multiple instantiations in a test<br/>bench multi-port Initiators or Targets)</li> </ul>          |

| <ul> <li>✤ Latest FC standards compliant</li> </ul>                                                                               | <ul> <li>Scalable for multiple instantiations in a<br/>testbench (multi-port Initiator/Target testing)</li> </ul>   |

| <ul> <li>Error Injections &amp; ability to enable or disable<br/>specific error checks and violations</li> </ul>                  | <ul> <li>Configurable test generation for constrained<br/>random, directed and error testing</li> </ul>             |

| <ul> <li>Programmable parameters through configurable<br/>Knobs</li> </ul>                                                        | <ul> <li>Ability to control and change packet value<br/>during transmission through each layer</li> </ul>           |

| <ul> <li>User configurable reports for logging events and transactions</li> </ul>                                                 | <ul> <li>Multiple Language Interface – SystemVerilog,<br/>Verilog, VHDL, C/C++, SystemC, 'e', VERA</li> </ul>       |

| <ul> <li>Automatic and user configurable Callback<br/>capability</li> </ul>                                                       | <ul> <li>Packet corruption at bit level granularity</li> </ul>                                                      |

| <ul> <li>Comprehensive Compliance Suite</li> </ul>                                                                                | <ul> <li>Supports OVM, UVM and VMM</li> </ul>                                                                       |

|                                                                                                                                   |                                                                                                                     |

DATASHEET Rev. 7

### **PRODUCT DETAILS**

#### **Initiator Model Features**

Fibre Channel Initiators Bus Functional Models comes with a wide range of configurable attributes provides engineers with a flexible, scalable Model to simulate real world environments.

- Initiator capable of connecting to multiple Targets.

- . Generates multiple FC Traffic data patterns including Random and User Defined

- Ability to Inject multiple Error conditions

- Sends specific or custom commands

- Capability to discover target information or skip discovery step and come up with appropriate target profile

- Performs Task Management functions

- Configurable login parameters and behavior

#### **Target Model Features**

Fibre Channel Target Bus Functional Models comes with a wide range of configurable attributes provides engineers with a flexible, scalable Model to simulate real world environments.

- Multiple error conditions and triggers allow for complex error injection.

- The ability to program complex and varying range of target configurations

- Supports block mode device

- Multiple LUN capability

- Responds to Fibre Channel traffic & specific or custom commands.

- Capable of responding to discovery commands such as INQUIRY, REPORT LUNS, etc

- Supports several queuing attribute models

- Configurable LUN parameters

- o Speed

- o Size

- o Personality

- o Errors

#### Interface Inspector Coverage Scoreboard Monitor Checker Verification Engine FC Initiator/ Transaction Target BFM Generator Switch Error DUT FC Injector Initiator/ or Callbacks Target **BFM** Randomizer API / Knobs 1 ÷ **FC Comprehensive Test Suite** SV/UVM Tests Directed Random Error

#### **Other Features**

- Direct backdoor access to HDD memory

- Supports multi LUN addressing

- Frame Level error detection

- Supports CRC checking on received frames and optional CRC checking or insertion for transmitted frames.

- Buffer-to-buffer credit management support

- Statistics-gathering block for Frame Level, FCP Statistics & N port Statistics

- Speed-negotiation block

- Programmable parity checking of transmit data

- Support Port Login and Process Login

- Extended Link Services stimulus/response

- Supports multiple outstanding IOs/exchanges

- Ordered Set Sequence Validation

- . Elasticity Buffer

- Controls for Dword/Primitive override

- FC Port State Machine & FC-AL2 State Machine

- Real time statistics and performance data

| FC SOLUTIONS                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------|

| Developed by PerfectVIPs to address different<br>system level FC architectures, the following FC<br>solutions are available. |

| Verification IP:<br>• FC Initiator VIP<br>• FC Target VIP<br>• FC Initiator/Target VIP<br>Compliance Suites:                 |

|                                                                                                                              |

**ALDEC CADENCE MENTOR SYNOPSYS**

PerfectVIPs Inc. 1762 Technology drive, #224, San Jose, CA 95110 T: 408 912 2316 F: 408 748 8838 E: sales@perfectvips.com For more information visit www.perfectvips.com

# SUPPORTED SIMULATORS